# Projeto de Circuito para Energy Harvesting para RF em Tecnologia CMOS 180 nm

Renan Daniel Dias Martins, Sandro Binsfeld Ferreira Universidade do Vale do Rio dos Sinos, São Leopoldo, Brasil renandm@edu.unisinos.br

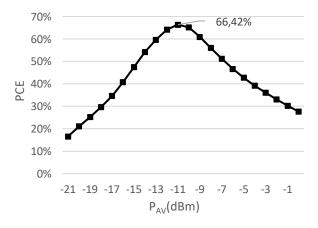

Resumo-Este trabalho apresenta um projeto de circuito integrado para conversão RF-CC utilizando uma tecnologia CMOS de 180 nm genérica para a frequência ISM (Industrial, Cientifica, Médica) de 13,563 MHz. O circuito proposto utiliza uma rede de elevação de tensão (VBN) com divisor de tensão capacitivo e um retificador multiplicador de tensão em topologia Cross-Coupled Charge Pump Rectifier (CC-CPR) modificado de dois estágios capaz de fornecer níveis de tensão de cerca de 2,3 V, para alimentação de dispositivos IoT, como sensores industriais ou dispositivos biomédicos. Esta tensão é alcancada para uma entrada de -11 dBm e carga de 100 k $\Omega$ , com eficiência de conversão de energia (PCE) de 66,42 %. O circuito proposto foi implementado e simulado em layout extraído usando o GPDK180 em Cadence® Virtuoso.

# I. INTRODUÇÃO

A popularização de aplicações inteligentes, como carros inteligentes, cidades inteligentes, entre outros, alavancada pelo crescente desenvolvimento tecnologias de IoT (Internet of Things - Internet das Coisas) fez com que uma ênfase maior fosse dada a um parâmetro de projeto, muitas vezes negligenciado em consumo comuns; de aplicações o Anteriormente, os principais motivadores de um projeto circuito integrado eram o desempenho, a confiabilidade e o custo. Quanto a este último item, o principal motivador de seu aumento em um projeto de dispositivo móvel é a fonte de energia; principalmente baterias. Além do custo, a evolução tecnológica das baterias não segue o mesmo ritmo de avanço que a evolução dos sistemas digitais [1], causando um gap entre estes setores e limitando a autonomia energética dos projetos.

Uma forma encontrada para resolver, ou mitigar os problemas intrínsecos ao uso de baterias é a geração local através da coleta de energia do ambiente ou, mais especificamente, um conceito chamado *Energy Harvesting* (EH, ou em tradução livre, Coleta de Energia). Este conceito permite que a energia possa ser gerada onde o sensor, o dispositivo móvel ou o equipamento, estiverem instalados. Algumas formas

conhecidas de EH são a energia solar, o calor, a energia das vibrações mecânicas e a energia das ondas de radiofrequência (RF).

Focando em RF, pode-se dizer que é uma forma de energia que começou a se tornar popular no meio científico-tecnológico há pouco tempo. Esta energia pode ser captada com a utilização de antenas de RF a partir das ondas eletromagnéticas presentes no ambiente e com a utilização de circuitos de condicionamento e retificação. Um fator diferencial para este tipo de EH é que o circuito pode ser projetado tanto para captar energia do espectro ambiente em uma determinada banda, como para captar energia de uma fonte geradora local sintonizada em uma frequência central específica. Nesse caso, diz-se que o dispositivo é iluminado por uma fonte de RF. As aplicações de circuitos de Radiofrequência para Energy Harvesting (RFEH) são impulsionadas principalmente desenvolvimento da IoT, da indústria 4.0 e de aplicações biomédica, principalmente engenharia biossensores.

O artigo está estruturado na seguinte forma: na Seção II é apresentado o circuito proposto; a Seção III discute os resultados de simulação de layout extraído, e a Seção IV apresenta as principais conclusões obtidas.

# II. ENERGY HARVESTING

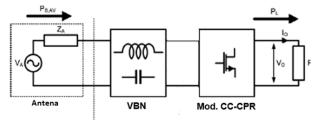

A Figura 1 apresenta um modelo de blocos do circuito desenvolvido. A etapa da antena é externa ao circuito e não foi projetada, apenas especificada.

Fig. 1. *Modelo do circuito proposto.*Fonte: Adaptado de [2]

A carga utilizada para os testes foi de 100 k $\Omega$ , como utilizada por  $^{[2][3]\,[7]}$  e  $^{[4]}.$

#### A. Voltage Boosting Network

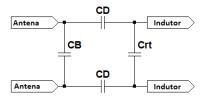

O circuito da rede de elevação de tensão implementado neste trabalho utiliza a mesma topologia proposta em [2], com otimização da rede de capacitores através de simulações.

Fig. 2. Rede de elevação de tensão.

Foram obtidas algumas combinações de valores ótimos para a rede. A rede dimensionada foi capaz (em simulação esquemática) de elevar a tensão de 27,5 mVpico para 2,9 Vpico, considerando uma antena bipolar de 12  $\Omega$  e indutância intrínseca de 9  $\mu$ H. A Equação 1, que define a capacitância de sintonia da rede, foi utilizada para chegar à capacitância total equivalente de 13,34 pF, pouco abaixo dos 13,63 pF da VBN proposta por  $^{[2]}$ .

$$C_T = C_B + \left(\frac{c_D.c_{R,T}}{c_{D} + 2c_{R,T}}\right) \tag{1}$$

Na equação (1),  $C_B$  é a capacitância de sintonia,  $C_D$  a capacitância do divisor de tensão capacitivo e  $C_{R,T}$  é capacitância de entrada de retificador. Para zerar o erro de offset na entrada, bastou fazer a ligação de um *choke* na entrada da rede, induzindo um curto em CC no circuito.

#### B. Retificador de tensão

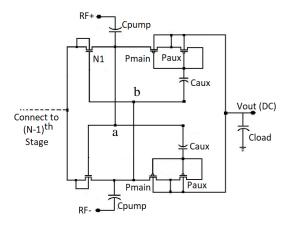

A definição do retificador de tensão utilizado partiu da análise e simulação do comportamento de topologias comumente utilizadas em EH, como topologias utilizando diodos *Schottky*, *Orthogonally Switching Charge Pump Rectifier*, *Cross-Coupled Charge Pump Rectifier* e uma modificação [1] desta última, que fora escolhida por apresentar os melhores resultados de conversão de energia e é apresentado na Figura 3. O CC-CPR modificado apresentou tensão de saída dez vezes maior que o retificador com diodos, 230 % maior que o OS-CPR e 60 % maior que o CC-CPR convencional.

O retificador CC-CPR apresenta simultaneamente uma baixa corrente de fuga e uma baixa resistência em estado "ligado". Ele consiste em um acoplamento CMOS diferencial cruzado em ponte  $^{[1]}$ . Neste retificador, a porta do transistor é polarizada por um sinal diferencial, observado nos nós "a" e "b". O transistor N1, na Figura 3, é polarizado diretamente no semiciclo negativo de  $V_A$ , enquanto  $V_B$  polariza diretamente N1 no semiciclo positivo. Isso faz com que a resistência e a tensão de limiar reduzam. Quando os semiciclos de  $V_A$  e  $V_B$  se invertem, o transistor se torna reversamente polarizado e a tensão de porta cai, aumentando a tensão de limiar e

reduzindo a corrente de fuga reversa. Assim, a tensão na saída de cada estágio é:

$$V_{DC(out)} = 2 \cdot V_{RF} - V_{drop} \tag{2}$$

Onde  $V_{DROP}$  é a perda no transistor e  $V_{RF}$  o sinal de entrada do circuito. Assim, nota-se que a máxima tensão obtida é  $2 \cdot V_{RF}$ . Arranjando os circuitos em cascata, observa-se um retificador multiplicador de tensão. Dessa forma tem-se:

$$V_{DC(out)} = \mathbf{N} \cdot (2 \cdot V_{RF} - V_{drop}) \tag{3}$$

O transistor  $P_{aux}$  acoplado nesta topologia modificada tem como finalidade o aumento do ganho do circuito, fazendo com que  $V_{TH}$  seja reduzida e o rendimento do circuito aumente. De acordo com <sup>[11]</sup>, esta topologia apresenta um rendimento 50% superior ao CC-CPR convencional com 12% de acréscimo de área de *chip*.

Fig. 3. OS-CPR Modificado [2].

Esta topologia apresenta muitas vantagens em relação às anteriores, mas a principal delas é a redução de V<sub>TH</sub> (tensão de limiar mínima para formação do canal <sup>[5][6]</sup>) causada pelo acoplamento do segundo transistor canal-p (P<sub>aux</sub>) configurado como diodo. A redução de VTH acarreta numa redução da "zona morta" de condução dos transistores, ou seja, VTH tendendo a zero, deixa toda a tensão disponível para condução, sem perdas causadas pela queda de tensão necessária para abertura do canal de condução do transistor.

A simulação do esquemático resultou em um nível de tensão suficiente para alimentar circuitos CMOS nesta tecnologia, chegando ao valor máximo de tensão na saída do circuito de 2,32 V para uma carga de  $100~\rm k\Omega$ . Este resultado apresentado considera uma entrada de -12 dBm na VBN, oriunda da antena do circuito.

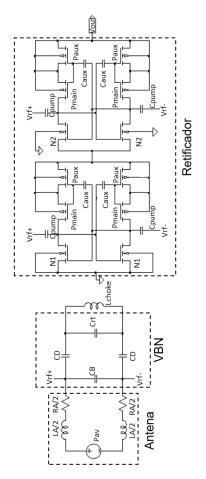

#### C. Circuito final

Através dos dados obtidos, definiu-se que a VBN utilizada para o trabalho seria composta por um capacitor de *boosting*, C<sub>B</sub>, de 250 fF, por dois capacitores divisores de tensão, C<sub>D</sub>, de 55 pF e por um capacitor de saída, C<sub>r,t</sub> de 25 pF. O retificador multiplicador utilizado foi definido como um CC-CPR modificado, conforme

proposto por <sup>[1]</sup>, de dois estágios de multiplicação com transistores com  $W=65,5~\mu m$  e L=220~nm, com multiplicidade igual a 4, divididos em 10 *fingers* de 6,55  $\mu m$  de comprimento. A antena definida para este trabalho apresenta resistência de 12  $\Omega$  e indutância de 9  $\mu H$ . A Figura 4 apresenta o circuito final projetado.

Fig. 4. Circuto completo do energy harvester.

## III. SMULAÇÕES E RESULTADOS

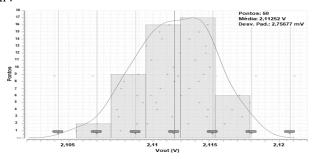

O circuito foi implementado em *layout* para simulação de componentes parasitas e avaliação de variações de processo e perdas por *mismatch*. A Figura 5 apresenta o resultado da análise de Monte Carlo do *layout* final implementado, apresentando uma pequena variação na tensão de saída com média 2,11 V e desvio padrão de 2,76 mV

Fig. 5. Análise de Monte Carlo para mismatch do layout final.

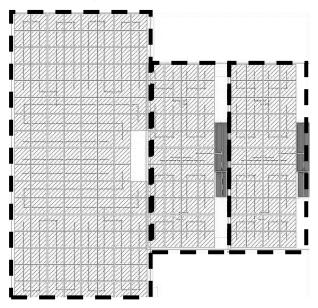

Essa baixa variação na tensão de saída devido às variações por *mismatch* se dá pelo arranjo feito nos componentes do circuito no *layout*. Utilizou-se uma técnica denominada centroide comum para distribuir os componentes de forma a minimizar a variação em sua magnitude conforme as possíveis variações do processo de fabricação. O *layout* implementado pode ser visualizado na Figura 6.

Fig. 6. Layout final.

O layout apresentado na Figura 6 conta com capacitores com células de mesmo tamanho, alinhadas e distribuídas simetricamente para mitigar os efeitos negativos de descasamento (mismatch). O retângulo maior à esquerda corresponde a VBN, com distribuição dos capacitores conforme as conexões visíveis. À direita é possível observar os retificadores em cascata. Os capacitores destes elementos também redimensionados para manter o alinhamento com os capacitores da VBN. À direita de cada retificador, podese observar o posicionamento dos transistores, basicamente em dois blocos, um abaixo, com os dois transistores canal-n envoltos por um guard ring tipo p e outro maior, acima, com quatro transistores canal-p envoltos por um guard ring tipo n.

O resultado da simulação do circuito após implementação do layout extraído com os mesmos parâmetros de carga, potência de entrada e frequência que o circuito simulado em esquemático apresentou uma redução na tensão final do circuito de quase 0,3 V, quando comparado ao resultado apresentado para a simulação esquemática. Além da tensão e da corrente na saída, é possível verificar que o *start up time* do circuito é de apenas 6 µs.

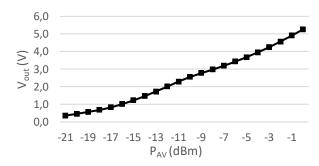

A Figura 7 apresenta a variação da tensão de saída do circuito de acordo com a potência injetada pela antena para uma carga na saída do circuito de  $100 \ k\Omega$ .

Fig. 7. Tensão de saída em função da potência de entrada do circuito.

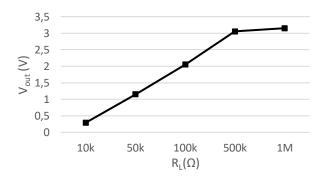

Outro parâmetro importante para o funcionamento do circuito é a carga acoplada. A Figura 8 apresenta a tensão de saída do circuito de acordo com a carga acoplada para uma entrada de -12 dBm. Como é possível observar, a variação da carga não provoca uma variação linear de tensão na saída em toda a curva. Percebe-se que, a partir de 1 M $\Omega$ , a tensão começa a estabilizar. Isso ocorre, pois a rede de elevação de tensão foi projetada para trabalhar no ponto ótimo em 100 k $\Omega$ . Quando a carga é modificada, a tensão de pico da VBN é alterada e o circuito se comporta de maneira diferente.

Fig. 8. V<sub>out</sub> em função da variação da carga em -12 dBm.

A eficiência máxima de conversão de potência (PCE) do circuito é alcançada para uma entrada de -11 dBm e uma carga de 100 k $\Omega$ . A Figura 9 apresenta a PCE do harvester em função da variação da potência disponibilizada pela antena.

Fig. 9. Eficiência de Conversão de Potência.

No pico da curva da Figura 9, observa-se uma eficiência de 66,42 %, que é um valor muito próximo à máxima eficiência de conversão esperada para esta topologia de retificação. Este resultado é particularmente interessante, pois mostra que o circuito, caso implementado fisicamente, poderia alcançar valores de eficiência realmente elevados, tornando-se uma opção plausível para aplicações IoT. Para fins de comparação, o CC-CPR modificado de [8] alcançou uma PCE de 65 % considerando apenas o estágio de retificação.

# IV. CONCLUSÃO

Neste trabalho, um conversor RF-CC foi apresentado para a frequência ISM de 13,563 MHz em uma tecnologia CMOS de 180 nm genérica. O circuito é constituído de uma rede de elevação de tensão com divisor de tensão capacitivo e um retificador em topologia *Cross-Coupled Charge Pump Rectifier* modificado, escolhido após comparação entre as topologias mencionadas neste trabalho e simulação Cadence® Spectre.

O circuito proposto por  $^{[1]}$ , e utilizado neste trabalho, apresentou uma redução de  $V_{TH}$ , que resultou numa conversão eficiente do sinal RF para um nível de tensão em corrente contínua. O circuito fornece uma tensão de saída de 2,3 V para uma entrada em -11 dBm e carga resistiva de 100 k $\Omega$ , com uma eficiência de conversão de potência total do circuito de 66,42 %. Com esta PCE e uma entrada na casa dos -11 dBm, o circuito é capaz de fornecer em torno de 51  $\mu W$  de potência para o circuito que estiver acoplado.

# REFERÊNCIAS

- [1] CHOUHAN, S. S.; HALONEN, K. A modified cross coupled rectifier based charge pump for energy harvesting using RF to DC conversion. Circuit Theory and Design (ECCTD), 2013 European Conference on, [s. l.], n. 1, p. 1–4, 2013.

- [2] MANSANO, A. R. Radio frequency energy harvesting and low power data transmission for autonomous wireless sensor nodes. 2016. Technische Universiteit Delft, [s. l.], 2016.

- [3] MANSANO, A.; BAGGA, S.; SERDIJN, W. A high efficiency orthogonally switching passive charge pump rectifier for energy harvesters. IEEE Transactions on Circuits and Systems I: Regular Papers, [s. 1.], v. 60, n. 7, p. 1959–1966, 2013.

- [4] POP-VADEAN, A. et al. Harvesting energy an sustainable power source, replace batteries for powering WSN and devices on the IoT. In: IOP CONFERENCE SERIES: MATERIALS SCIENCE AND ENGINEERING 2017, Anais... [s.l: s.n.].RAPPAPORT, T. S. Wireless Communications: Principles and Practice. 2. ed. Upper Saddle River: Prentice Hall, 2002.

- [5] RAZAVI, B. Design of Analog CMOS Integrated Circuits. McGraw Hill, [s. l.], v. 6, n. 7, 2016.

- [6] SEDRA, A. S.; SMITH, K. C. Microeletrônica. 5. ed. São Paulo: Pearson Prentice Hall, 2007.

- [7] UDUPA, S. S.; SUSHMA, P. S.; CHAITHRA. An orthogonally switching charge pump rectifier for RF energy harvester. In: RTEICT 2017 - 2ND IEEE INTERNATIONAL CONFERENCE ON RECENT TRENDS IN ELECTRONICS, INFORMATION AND COMMUNICATION TECHNOLOGY, PROCEEDINGS 2018, Anais... [s.l: s.n.]

- [8] DAI, H. et al. A review and design of the on-chip rectifiers for RF energy harvesting. In: 2015 IEEE INTERNATIONAL WIRELESS SYMPOSIUM, IWS 2015 2015, Anais... [s.l: s.n.]